- RS Stock No.:

- 145-0091

- Mfr. Part No.:

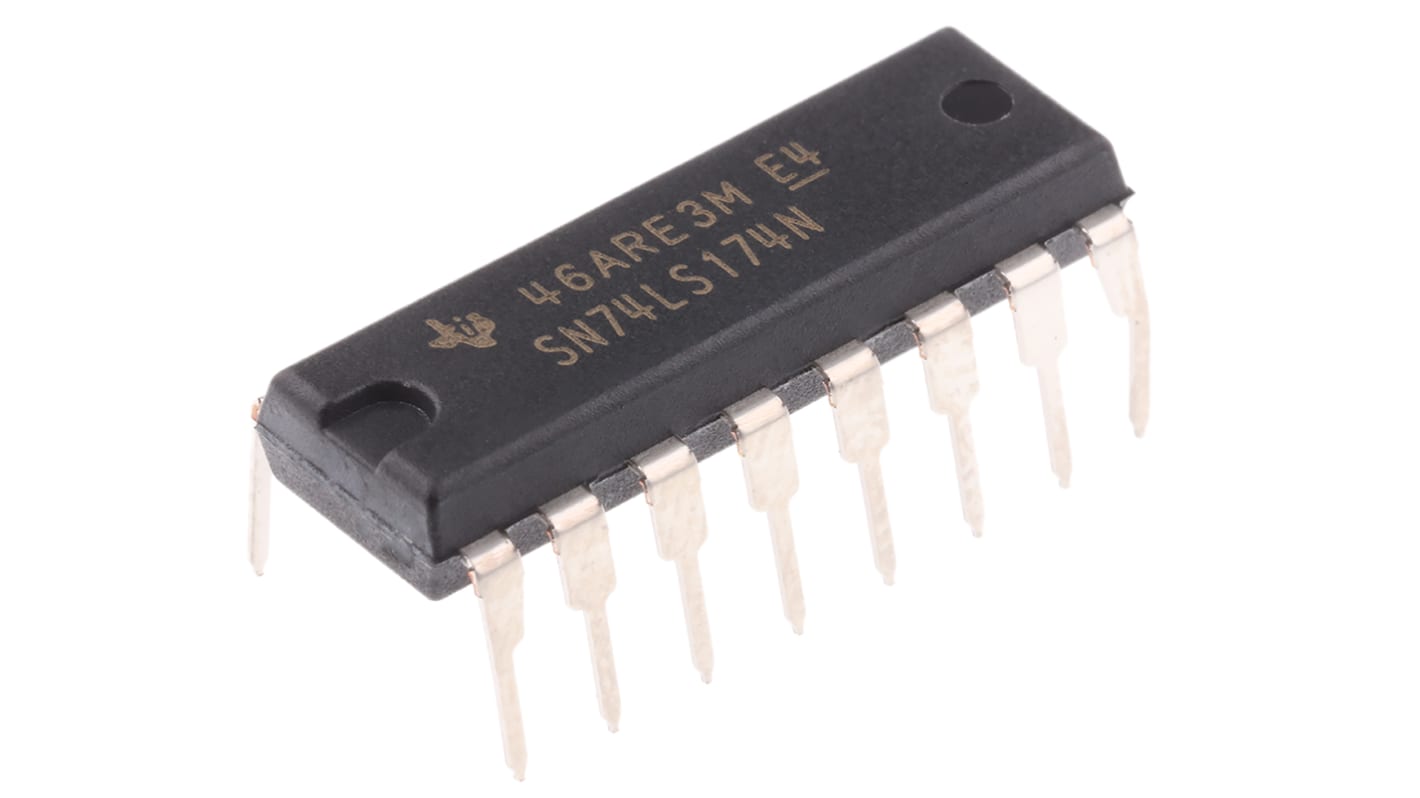

- SN74LS174N

- Manufacturer:

- Texas Instruments

Discontinued product

- RS Stock No.:

- 145-0091

- Mfr. Part No.:

- SN74LS174N

- Manufacturer:

- Texas Instruments

Technical data sheets

Legislation and Compliance

Product Details

74LS Family Flip-Flops & Latches, Texas Instruments

Texas Instruments range of Flip-Flops and Latches from the 74LS Family of Low Power Schottky Logic ICs. The 74LS Family use bipolar junction technology coupled with Schottky diode clamps to achieve operating speeds equal to the original 74TTL family but with much lower power consumption.

74LS Family

Specifications

Attribute | Value |

|---|---|

| Logic Family | LS |

| Logic Function | D Type |

| Input Type | Single Ended |

| Output Signal Type | Single Ended |

| Triggering Type | Positive Edge |

| Polarity | Non-Inverting |

| Mounting Type | Through Hole |

| Package Type | PDIP |

| Pin Count | 16 |

| Set/Reset | Master Reset |

| Number of Elements per Chip | 6 |

| Maximum Propagation Delay Time @ Maximum CL | 30 ns @ 5 V |

| Dimensions | 19.3 x 6.35 x 4.57mm |

| Maximum Operating Supply Voltage | 5.25 V |

| Width | 6.35mm |

| Minimum Operating Temperature | 0 °C |

| Minimum Operating Supply Voltage | 4.75 V |

| Maximum Operating Temperature | +70 °C |

| Propagation Delay Test Condition | 15pF |

| Length | 19.3mm |

| Height | 4.57mm |